RZ/G2L-Based MYD-YG2LX System Startup Time Optimization Application Notes

2025-06-23

613

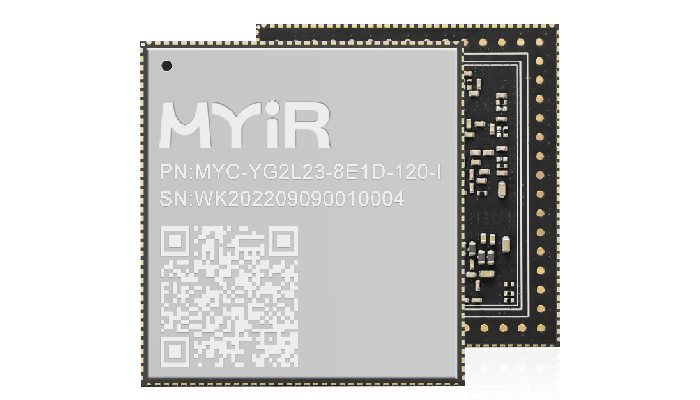

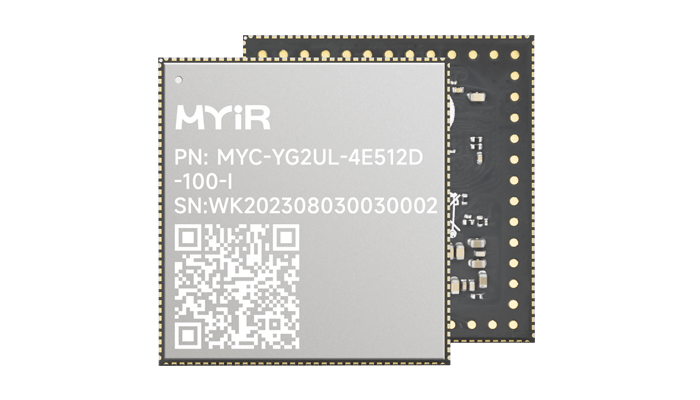

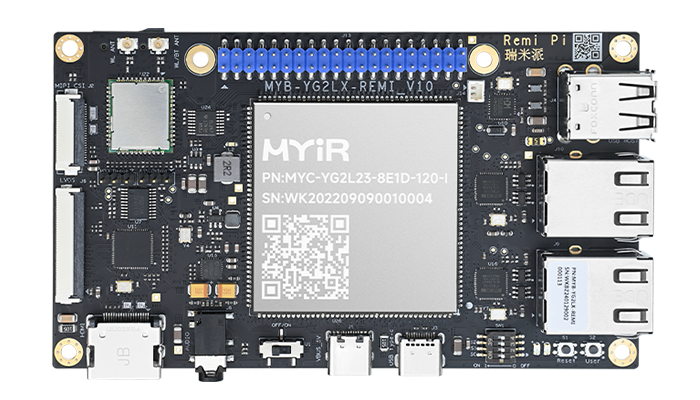

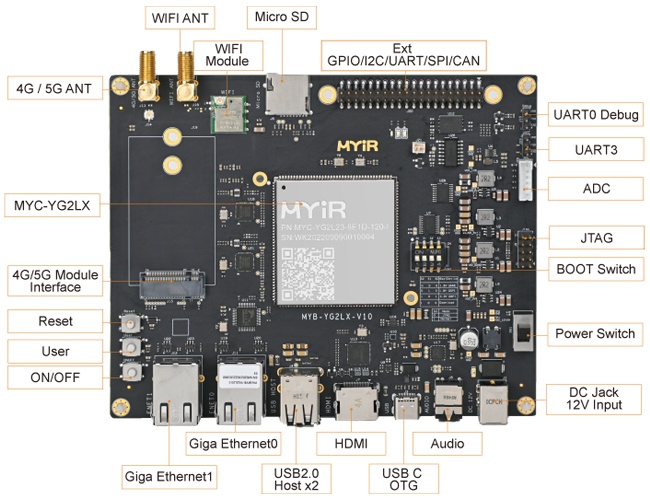

The MYD-YG2LX development board is powered by the Renesas RZ/G2L processor. The processor features a dual-core Cortex-A55 operating at 1.2GHz and a Cortex-M33 core at 200MHz, an integrated high-performance Mali-G31 GPU (operating at 500MHz) for 3D graphics acceleration, as well as a video processing unit that supports H.264 hardware encoding and decoding. The processor also includes a 16-bit DDR4-1600 / DDR3L-1333 memory controller, Gigabit Ethernet, USB, CAN, SD card, MIPI-CSI, and a range of other peripheral interfaces. With its rich features and robust performance, the MYD-YG2LX is well-suited for applications in industrial automation, medical equipment, and power systems.

This article introduces a debugging case for optimizing system boot time based on the MYD-YG2LX development board. Common boot methods include removing the conventional u-boot and directly using SPL to load the kernel, as well as retaining the conventional u-boot to load the kernel. Currently, the MYD-YG2LX adopts the method of retaining conventional U-Boot for booting, with a boot time exceeding 20 seconds. The subsequent discussion mainly covers time optimization for TFA, U-Boot, kernel, and the file system.

1. Hardware Resources

One USB-to-TTL debug serial cable

One MYD-YG2LX development board

One 12V power adapter

2. Software Resources

Linux virtual machine

Cross-compilation toolchain provided by MYIR

Linux kernel version 5.10.83

3. Environmental Preparation

Before debugging, it is necessary to install the Linux virtual machine and other related development environments.

For details, please refer to Chapter 2.0 of the “MYD-YG2LX-Linux Software Development Guide”.

4. Boot Time Optimization

4.1 TF-A Optimization

The TF-A boot log primarily includes the following.

If you find these logs untidy, you can dive into the TF-A source code, use grep command to search for key information and print it out, then remove the related prints. This may require some effort to find.

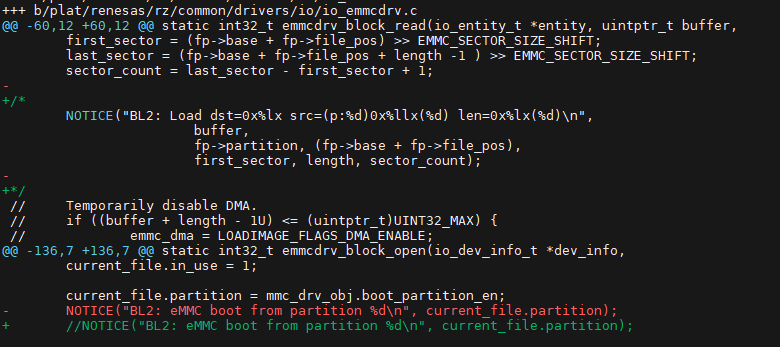

For example, (grep rn "BL2:") search for the key file (the following image is just one of the places), and then block it.

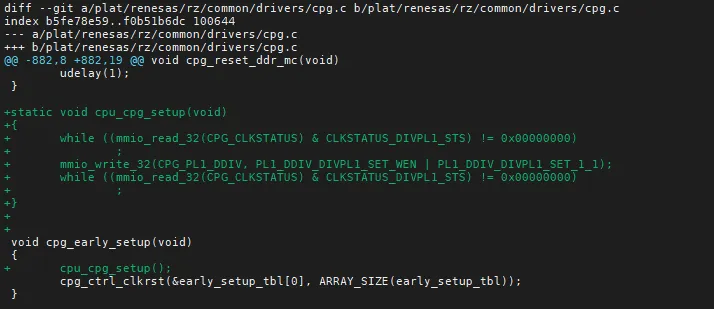

In addition, you need to check whether the following register is configured in the source code. If it is already set, you can ignore it; if not, it should be enabled, as this can help reduce the system boot time.

static void cpu_cpg_setup(void)

{

while ((mmio_read_32(CPG_CLKSTATUS) & CLKSTATUS_DIVPL1_STS) != 0x00000000);

mmio_write_32(CPG_PL1_DDIV, PL1_DDIV_DIVPL1_SET_WEN | PL1_DDIV_DIVPL1_SET_1_1);

while ((mmio_read_32(CPG_CLKSTATUS) & CLKSTATUS_DIVPL1_STS) != 0x00000000);

}

void cpg_early_setup(void)

{

cpu_cpg_setup();

cpg_ctrl_clkrst(&early_setup_tbl[0], ARRAY_SIZE(early_setup_tbl));

}

Finally, compile TFA and update it.

4.2 u-boot Optimization

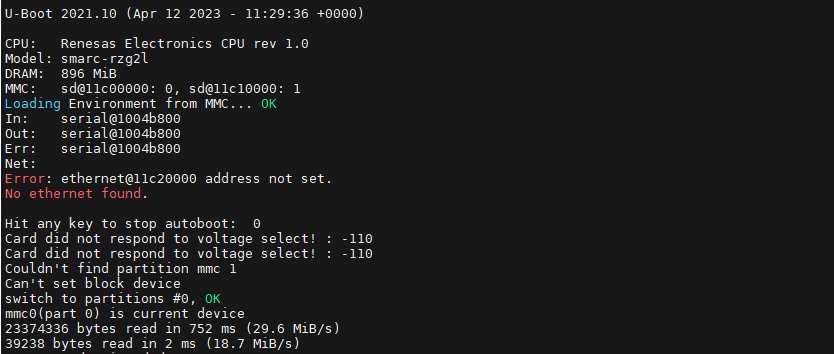

The normal boot logs are as follows. We need to optimize this part, focusing on the following three points:

Crop uboot to reduce its size.

The 2G DDR configuration file for MYD-YG2LX platform can be found in configs/myc-rzg2l_defconfig, while the 1G DDR configuration file can be found in configs/myc-rzg2l_dddr1gb_defconfig. You can disable some unnecessary features in this configuration file, which need to be removed according to the actual situation. For example:

Remove the countdown time for bootdelay

Bootdelay usually defaults to 2-3 seconds. To remove it, you can directly modify the include/config/myc-rzg2l. h file, for example:

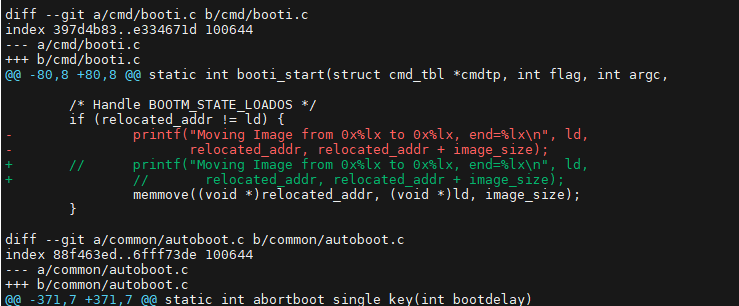

Close the print log of uboot

To disable the printing of logs related to uboot, you can search for key information in the source code path of uboot and then block it (the following diagram is just one of the places), for example:

Finally, compile and update uboot.

4.3 Kernel Optimization

The typical modifications of Kernel mainly include the following:

Simple: Reduce console messages by adding quiet in CMDline

Moderate: Simplify the kernel by removing drivers, file systems, and subsystems, reducing the time it takes to decompress or load the kernel

Moderate: Simplify device tree by removing unused hardware interfaces

Challenging: Starting to optimize drivers with poor behavior is a relatively complex and difficult task. Optimizing the driver program can improve its performance, stability, and compatibility, thereby enhancing the overall performance of the system. However, if the driver behaves poorly, such as crashing, lagging, or conflicting, then optimizing becomes even more challenging and tricky. This requires in-depth analysis and fixing of driver issues, adjusting its code and algorithms to make it more efficient and reliable.

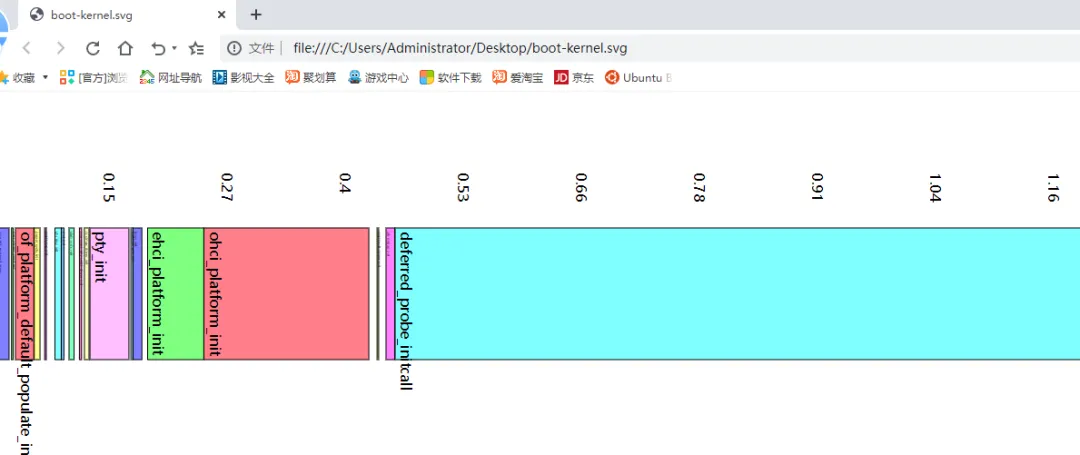

Use Bootgraph to analyze the call time of kernel startup, remove time-consuming drivers, and optimize the drivers needed.

In short, optimization is still a quite complex project. This time, we will mainly optimize from the following points:

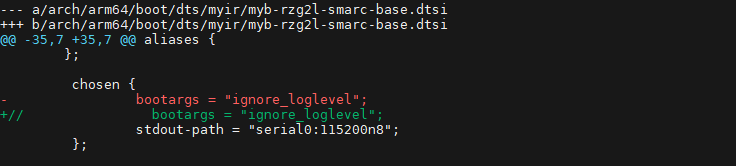

To remove the print level of the kernel, it is necessary to disable the log attribute in the kernel source code and increase the log level in the uboot source code. The kernel modification is as follows:

Uboot has been modified as follows:

Turn off some unnecessary peripheral resources in the kernel and reduce the kernel size (modifications need to be made according to one's own situation)

You can block some unnecessary interfaces in the device tree and block some unnecessary driver configurations in the kernel configuration file, for example:

Use Bootgraph to analyze the call time of kernel startup, remove time-consuming drivers, and optimize the drivers needed.

Firstly, it is necessary to add a timestamp and init debug call to uboot:

setenv bootargs 'rw rootwait earlycon root=/dev/mmcblk0p2 printk.time=1 initcall_debug=1'

Then start the kernel and collect the startup log, as follows:

dmesg > boot-kernel.log

Return to the kernel source code directory, enter the kernel source code scripts directory, and use the following

command to generate a visual graphic, as follows:

./bootgraph.pl boot-kernel.log > boot-kernel.svg

Then open boot.svg to view the most time-consuming driver calls, close those that are useless, and optimize those that are needed.

Finally, compile and update the kernel.

4.4 File System Optimization

The file system of MYD-YG2LX is built on Yocto. For information on how to build Yocto, please refer to Chapter 3.0 of the “MYD-YG2LX-Linux Software Development Guide”.

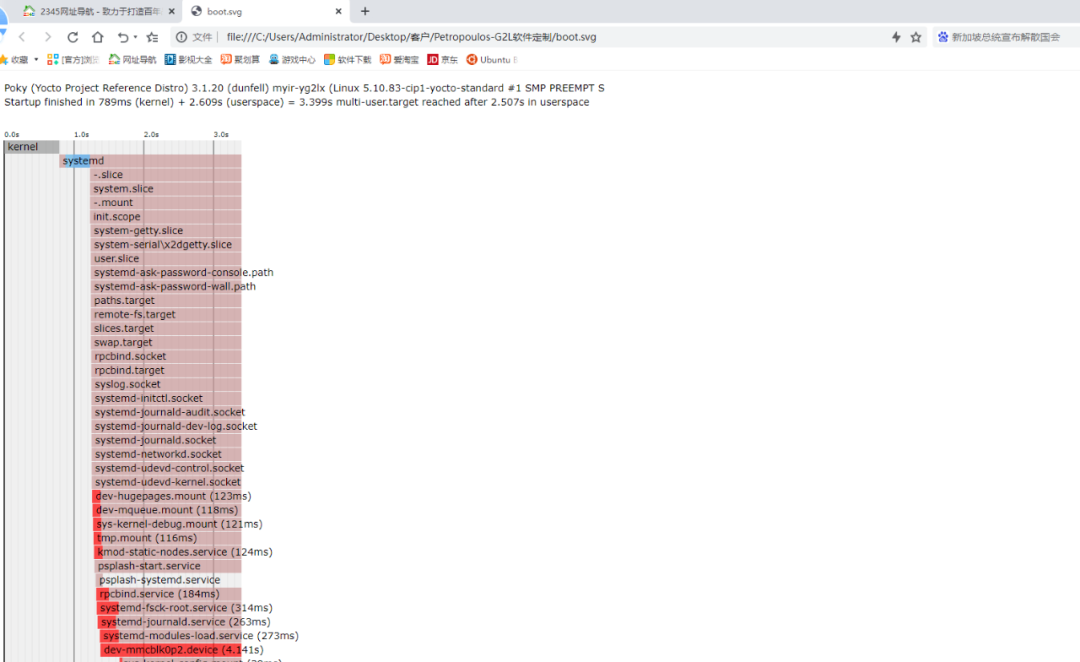

The file system can mainly use the following three commands to find the service that takes the most time, and then optimize it according to the actual situation. Of course, all services can also be presented in graphical form, which is more intuitive. By using systemd-analyze plot>boot.svg, the startup sequence and consumption time of each service can be displayed. For these services, unnecessary ones can be removed or the startup sequence between services can be adjusted.

Systemctl list unit files -- state=enabled # View all boot up services

Systemd analyze blade # View service initialization time

Systemd analyze critical chain # View the ones that take the most startup time

4.5 Start testing

After the above optimization, a SD card flashing package can be packaged and flashed to the EMMC of the board. For how to package it, please refer to Chapter 4.3 of the "MYD-YG2LX Linux Software Development Guide". Finally, start the test and execute systemd-analyze to see the startup time. The effect is as follows:

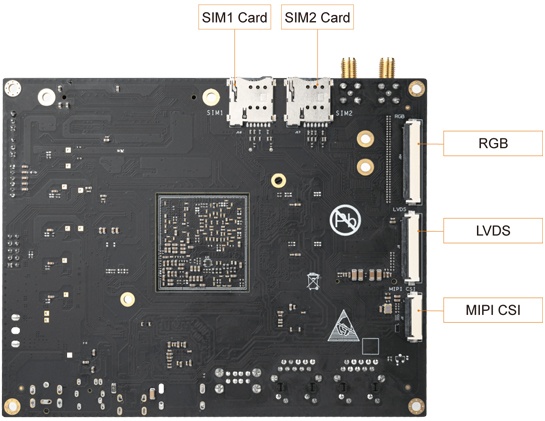

The MYD-YG2LX Development Board is built around the MYC-YG2LX System-On-Module. Its base board provides rich communication interfaces such as four Serial ports, two Gigabit Ethernet, two USB 2.0 HOST and one USB 2.0 OTG, one Micro SD card slot, one M.2 Socket for USB based 4G/5G LTE Module with two SIM card holders, one USB2.0 based WiFi module, one GPIO/I2C/UART/SPI/CAN extension header, etc. It also supports various multi-media interfaces including Audio input/output, MIPI-CSI camera interface as well as HDMI, LVDS and RGB video output interfaces.

MYD-YG2LX Development Board Top-view

MYD-YG2LX Development Board Bottom-view

2025-11-27

SECC GreenPHY Solution: Bridging STM32MP135 SOM to V2G Industry Advancement

Debug MSE102x G on MYC-YF13X, providing reference for V2G communication development.

2025-11-20

SECC Solution for Charging Pile Applications

MYIR's SECC solution delivers a high-standard, low-risk rapid development platform for clients, with core strengths in protocol compatibility, operational security, and a comprehensive reference design.

2025-11-02

Simultaneous Control of 4 YOLOv8 Video Streams via MYIR's RK3576 Board

In the era of rapid technological advancement, the integration of artificial intelligence and edge computing is transforming our lives at an unprecedented pace. The RK3576 processor features a quad-co

2025-09-20

Compiling OpenCV and Developing Applications on the RK3576 Board

This article introduces how to compile OpenCV on the RK3576 development board and build an application.

2025-08-30

MYIR T536 Development Board: Multi-protocol IoT Gateway Solution Test

The article details the development and testing of a multi-protocol IoT gateway solution that utilizes MYIR's MYD-LT536 development board, which is based on the Allwinner T536 SoC.

2025-08-29

MYIR RK3576 Development Board: 12-Channel 1080p HD Video Streaming

MYIR has successfully achieved efficient H.264 encoding and low-latency RTSP streaming for 12-channel HD video streams on the Rockchip RK3576 SOM.

2025-08-07

Compiling Kernel for MYD-LMX9X Development Board

This guide walks you through building a Linux kernel for the MYIR MYD-LMX9X Development Board

2025-06-23

How to Implement an Environmental Monitoring System on the STM32MP257 Board

This article introduces how to use MYIR's MYD-LD25X development board (MYIR's STM35MP257-based development board) to implement a simple environmental monitoring system.

2025-06-17

OpenCV Pedestrian Detection Application Solution Based on MYIR's T527 Development Board

In this article, we will introduce the testing of OpenCV pedestrian detection solution based on MYIR's MYD-LT527 Development Board (based on Allwinner T527 processor).